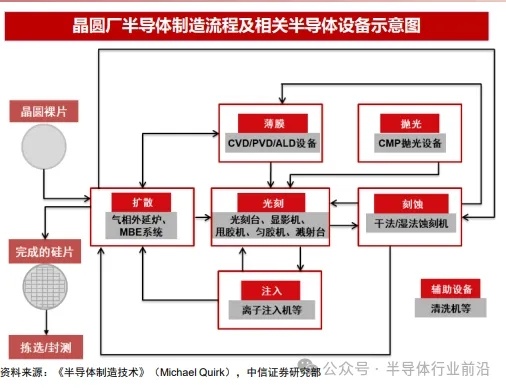

晶圆厂内半导体设备按照类型可大致分为薄膜沉积、光刻、刻蚀、 过程控制、自动化制造和控制、清洗、涂布显影、去胶、化学机械研磨(CMP)、快速热处理/氧化扩散、离子注入、其他晶圆级设备等类别,其中薄膜沉积、光刻、刻蚀、过程控制占比最大。

图1:晶圆厂半导体制造流程及相关半导体设备示意图

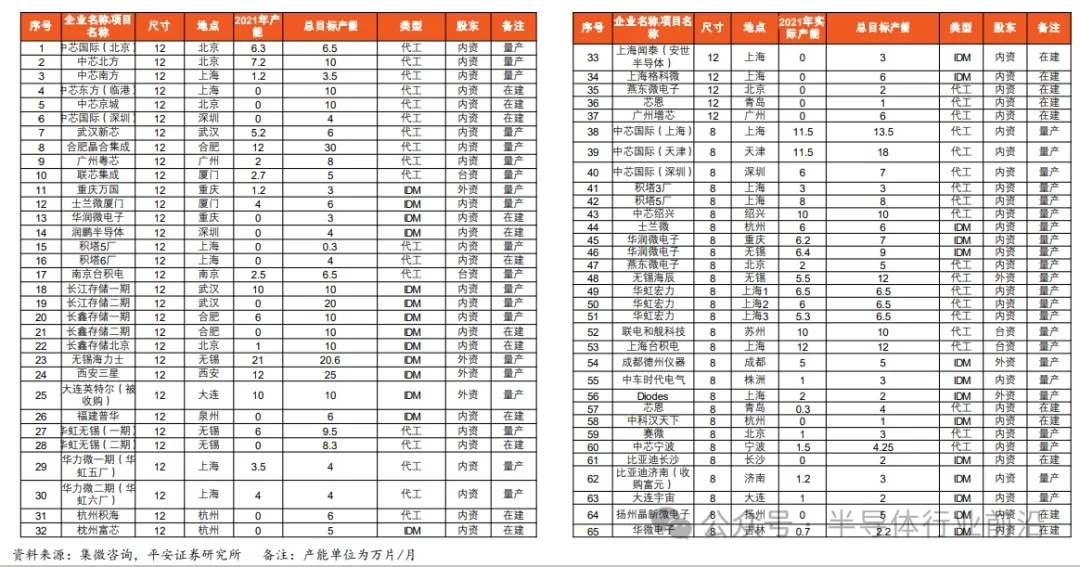

图2:大陆主要晶圆厂扩产一览

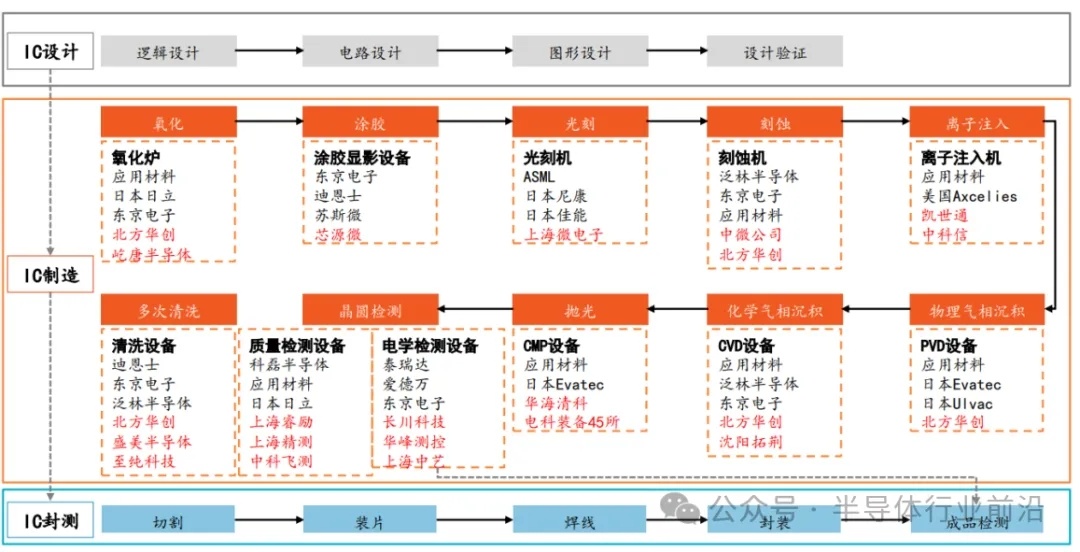

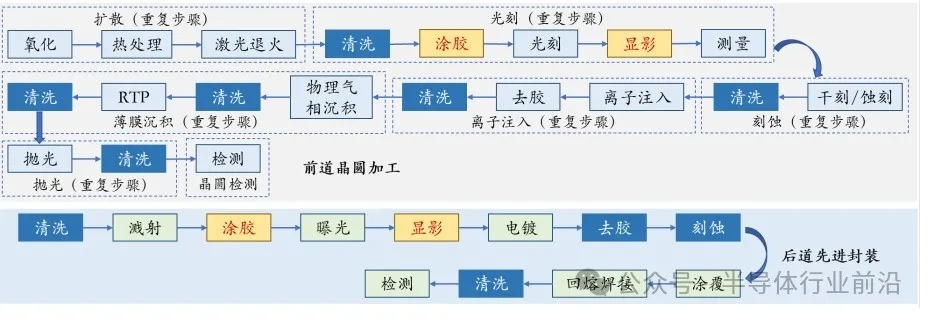

图3:半导体制程工艺流程及设备

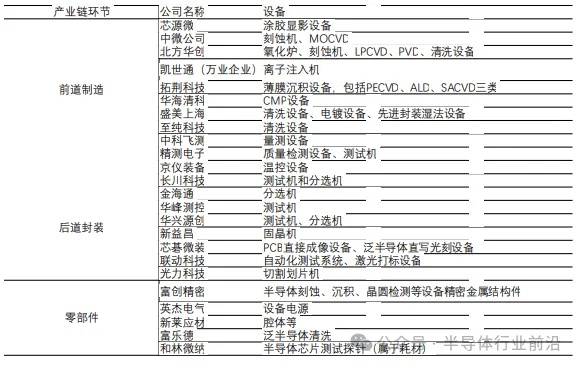

国产半导体设备商积极推进上市进程。科创板以来已有多家半导体设备公司上市,包括中微公司、芯碁微装、盛美上 海、华海清科和拓荆科技等。主要的上市公司如下:

PVD&CVD沉积设备:

薄膜沉积技术按工艺原理的不同可分为物理气相沉积(PVD)、化学气相沉积(CVD)和原子层沉积 (ALD)。①PVD:指在真空条件下采用物理方法将材料源(固体或液体)表面气化成气态原子或分子, 或部分电离成离子,并通过低压气体(或等离子体)过程,在基体表面沉积具有某种特殊功能的薄膜的技 术。②CVD:是通过化学反应的方式,利用加热、等离子或光辐射等各种能源,在反应器内使气态或蒸汽 状态的化学物质在气相或气固界面上经化学反应形成固态沉积物的技术,是一种通过气体混合的化学反应 在基体表面沉积薄膜的工艺。③ALD:是利用反应气体与基板之间的气—固相反应,来完成工艺的需求。

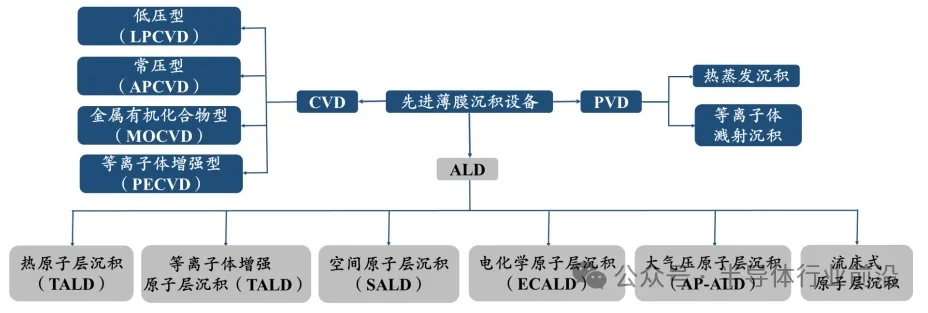

图4:薄膜沉积设备技术分类

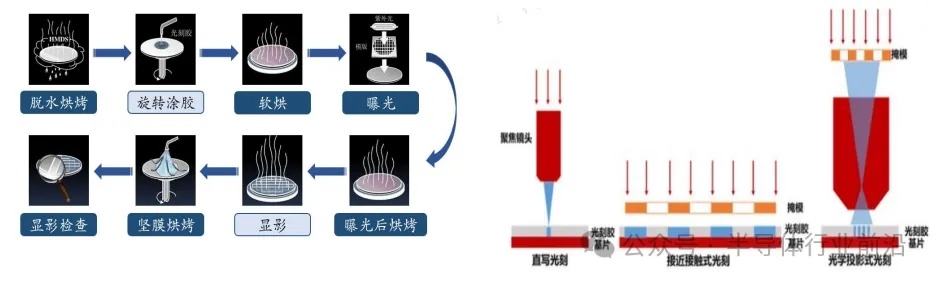

涂胶显影:涂胶显影设备与光刻机紧密协作,是光刻工序中的核心设备。涂胶显影设备主要包括涂胶 机、喷胶机和显影机,其中涂胶机&喷胶机应用于曝光前光刻胶涂覆,显影机应用于曝光后图形显影。涂胶 显影设备分别连接光刻机的输入&输出端口,直接影响光刻图形质量&缺陷控制,并对后续的蚀刻、离子注 入等工序中的图形转移也有较大影响。后道先进封装中的涂胶显影设备精度要求低于前道晶圆加工。①前道晶圆加工:以8/12英寸设备为主,主要 与光刻机配合完成晶圆加工过程中的精细光刻工艺流程,对设备精度要求极高;②后道先进封装:主要用于 Bump、WLCSP、Fanout 等后道先进封装技术的涂胶、显影等工序,对设备精度的要求低于前道晶圆加工。

图5:涂胶显影是光刻环节的核心工序之一

光刻机

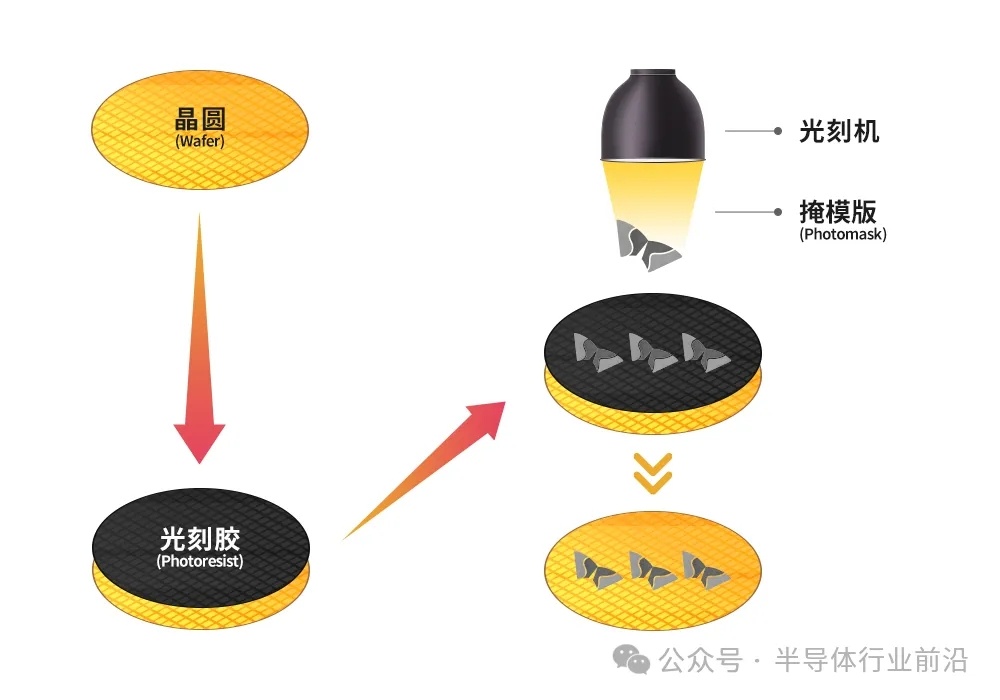

半导体制造商把上面我们所说的制作饼干模具(遮盖物)的过程叫做光刻工艺。光刻工艺的第一步就是涂覆光刻胶(Photoresist)。光刻胶经曝光后化学性质会发生变化。具体而言,就是在晶圆上涂覆光刻胶后,用光(激光)照射晶圆,使光刻胶的指定部分的性质发生改变。

图6-1:光刻工艺基本步骤

如果直接用激光照射整个晶圆,那么光刻胶的所有部分都会发生质变,所以需要使光源通过特定形状的母版,再照射到晶圆上,这个母版就叫掩模版(Photomask)。光源通过掩模版照射到晶圆上,即可将掩模版的图案转印到晶圆上。

在晶圆上绘制图形后,还要经显影(Develop)处理,即在曝光后,除去曝光区光刻胶化学性质发生变化的部分,从而制作出所需的“饼干模具”。简言之,光刻工艺可以概括为使光源通过掩模版照射到涂敷光刻胶的晶圆表面,以将掩模版图形转印到晶圆上的工艺。

先进封装中光刻机主要应用于凸块、RDL、 TSV等电极接触点的制作。与在前道制造中用 于器件成型不同, 在先进封装中主要用做金属电极接触,例如TSV打孔实现堆叠芯片之间的垂直互联互通, 钻孔就需要光刻与刻蚀的配合完成;凸块上实现在芯片特定位置的电镀,也需要光刻把Bump的位置打出 来;在RDL图形转移和再连接,是通过掩模版然后光刻机曝光将图形打到芯片上。 目前,在泛半导体领域,根据是否使用掩膜版,光刻技术主要分为直写光刻与掩膜光刻。其中,掩膜光刻 可进一步分为接近/接触式光刻以及投影式光刻。

图6-2:光刻工艺流程直写光刻、接近/接触式光刻以及投影式光刻示意图

刻蚀机:

刻蚀工艺是选择性地从晶圆表面去除不需要的材料以达到集成电路芯片制造要求 的工艺过程,用于去除光刻胶(Photo Resist,PR)未覆盖的底部区域,仅留下所需的图案。这一工艺流程旨在将掩模(Mask)图案固定到涂有光刻胶的晶圆上(曝光→显影)并将光刻胶图案转印回光刻胶下方膜层。刻蚀工艺按照对晶圆的选择性去除区域可以分为图案刻蚀(pattern)与无图案刻蚀(blanket)两类。图案刻蚀是在指定区域选择性地刻蚀材料,从而将晶圆表面上的光刻胶或硬掩模的图案转移到下方的薄膜上。无图案刻蚀则是去除晶圆表面全部或者部分薄膜。刻蚀工艺如果按照工艺方法分为3种:纯化学刻蚀、纯物理刻蚀以及介于两者之间的反应离子刻蚀(ReactiveIonEtch,RIE)。

刻蚀按工艺方法的分类:

其中,湿法刻蚀是纯化学刻蚀工,没有物理轰击过程,仅通过化学反应除去材料。湿法刻蚀化学反应的副产物是气体、液体或可溶于刻蚀剂溶液的物质。在完成湿法刻蚀工艺之后,通常需要对晶圆进行冲洗和干燥。由于通常具有很好的刻 蚀选择性,因此纯化学刻蚀工艺可用于薄膜去除工艺,例如,光刻胶、氮化硅、垫层氧化 物、掩蔽氧化层和牺牲层氧化物的去除。

氩溅射刻蚀工艺是纯物理刻蚀。它广泛用于介质层溅射回刻工艺中,可以逐渐减小 开口,从而在后续材料沉积过程中更容易填充间隙。由于氩气是惰性气体,因此在溅射 过程中不会发生化学反应。

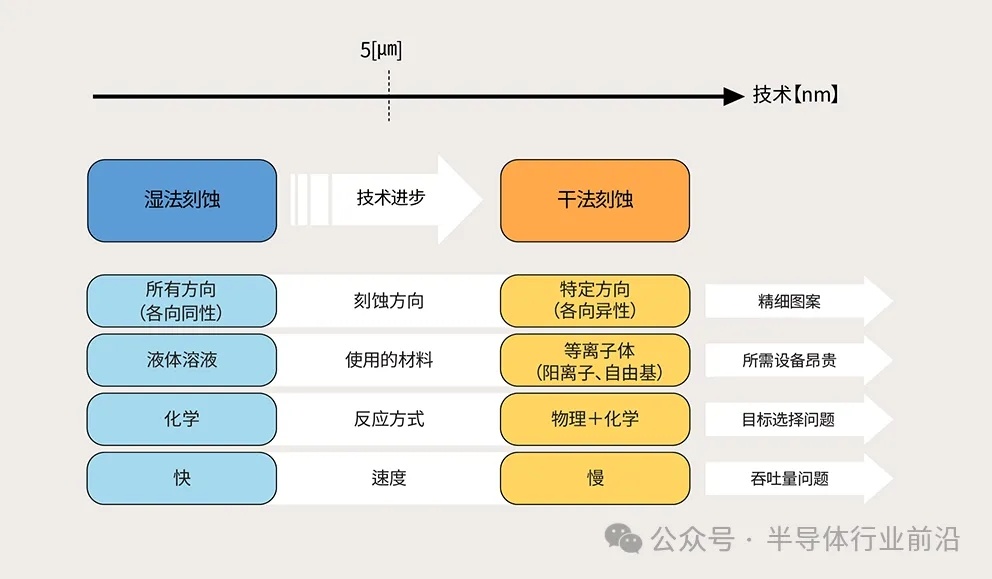

RIE的准确名称应该是离子辅助刻蚀(ion-assistedetch),因为这种刻蚀工艺中的离 子不一定是反应性的。先进的集成电路芯片制造中几乎所 有的图案刻蚀工艺都是 RIE工艺。随着电路的关键尺寸(Critical Dimension, CD)小型化(2D视角),刻蚀工艺从湿法刻蚀转为干法刻蚀。那你知道为什么会有这种进步么?下面给出讲解:

图7-1:干法和湿法刻蚀的比较

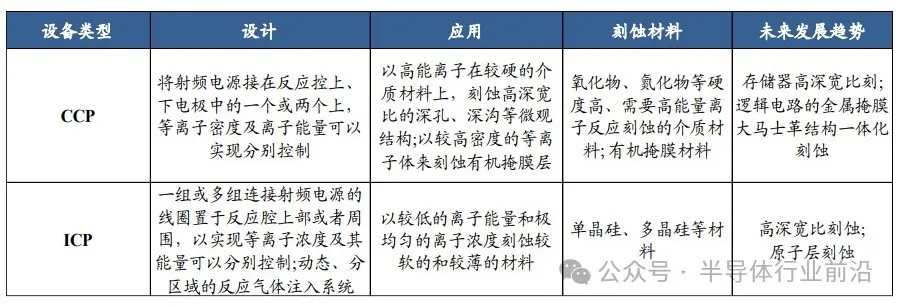

先进封装中, TSV中需要刻蚀打孔, RDL中需要刻蚀去除多余的UBM等,均有广泛应 用。干法等离子体刻蚀可分为电容性耦合等离子体刻蚀(CCP)和电感性耦合等离子体刻蚀(ICP)。两者激发和控制等离子体的方式不同,CCP为电容极板激发等离子体,ICP由电感线圈激发等离子体;ICP和CCP刻蚀的应用场景有所不同,CCP刻蚀设备主要以等离子体在较硬的介质材料上,刻蚀通孔、 沟槽等微观结构,ICP刻蚀设备主要以等离子体在较软和较薄的材料上,刻蚀通孔、沟槽等微观结构。

图7-2:ICP和CCP刻蚀设备分类图

CMP抛光机:

抛光工艺分类如下:

(1)机械抛光法。机械抛光的原理与磨片工艺相同,但其采用的磨料颗料更细些。机械抛光的硅片一般表面平整度较高,但损伤层较深,若采用极细的磨料抛光则速度很慢。目前工业上一般已不采用机械抛光法。

(2)化学抛光法。化学抛光常用硝酸与氢氟酸的混合腐蚀液进行。经化学抛光的硅片表面可以做到没有损伤,抛光速度也较快,但平整度相对较差,因此在工业生产中化学抛光一般作为抛光前的预处理,而不单独作为抛光工艺使用。

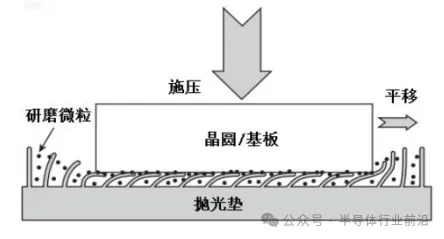

(3)化学-机械抛光法。化学-机械抛光法(CMP)利用抛光液对硅片表面的化学腐蚀和机械研磨同时作用,兼有化学抛光和机械抛光两种抛光法的优点,是现代半导体工业中普遍采用的抛光方法。化学-机械抛光法所采用的抛光液一般是由抛光粉和氢氧化钠溶液酿成的胶体溶液,抛光粉通常为SiO2。

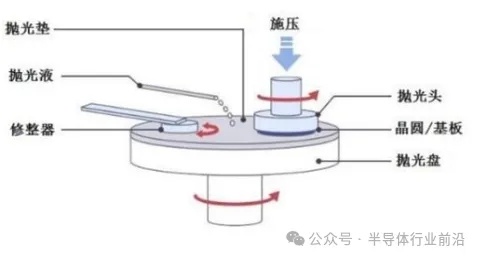

由于目前集成电路元件普遍采用多层立体布线,集成电路制造的前道工艺环节需要 进行多层循环。在此过程中,需要通过CMP工艺实现晶圆表面的平坦化。CMP就是能有效令集成电路的“楼层”达到纳米级全局平整的一种关键工艺技术。集成电路制造是CMP设备应用的最主要的场景,重复使用在薄膜沉 积后、光刻环节之前;除了集成电路制造,CMP设备还可以用于硅片制造环节与 先进封装领域。

抛光机的结构如图所示。贴有硅片的平板安装在抛光机上盘的下面,上盘可以升降和调整压力,下盘是一个直径很大的圆盘,内部需要通水冷却,表面覆盖韧性多孔的聚酯或聚氨酯质的抛光布。抛光时下盘在电动机带动下转动,粘有硅片的平板可绕自己的轴转动,以保证抛光的均匀,抛光液从下盘中央注入,在离心力的作用下向周围散开。抛光过程中由测温仪控制盘温。抛光液中的氢氧化钠起到化学腐蚀的作用,使硅片表面生成硅酸钢盐,通过二氧化硅胶体,对硅片产生机械摩擦,随之又被抛光液带走。这样就实现了去除表面损伤面的抛光作用。

图7-1:CMP抛光模块示意图

图7-2:CMP抛光作业原理图

对直径为200mm及更小的硅片来说,仅对上表面进行抛光,背面仍保留化学刻蚀后的表面,这就会在背面留下相对粗糙的表面,大约要比经过化学-机械抛光后的表面粗糙3倍左右。它的目的是提供一个粗糙表面来方便器件传送。

对直径为 300mm 的硅片来说,一般用化学-机械抛光法进行双面抛光(DSP)。硅片在抛光盘之间行星式的运动轨迹在改善表面粗糙度的同时,也使硅片表面平坦且两面平行。抛光后硅片的两面会像镜子一样,抛光后的硅片如图所示。

随着先进制程工艺逐渐逼近物理极限,越来越多厂商的研发方向由“如何把芯片 变得更小”转变为“如何把芯片封得更小”,先进封装快速发展。先进与传统封装最大区别在于芯片与外部电连接方式, 先进封装省略引线,采取传输速度更快的凸块、中间层等,主要包括凸块( Bump )、倒装(Flip Chip)、晶圆级封装 (Wafer level package)、再分布层技术(RDL)和硅通孔(TSV)技术等。

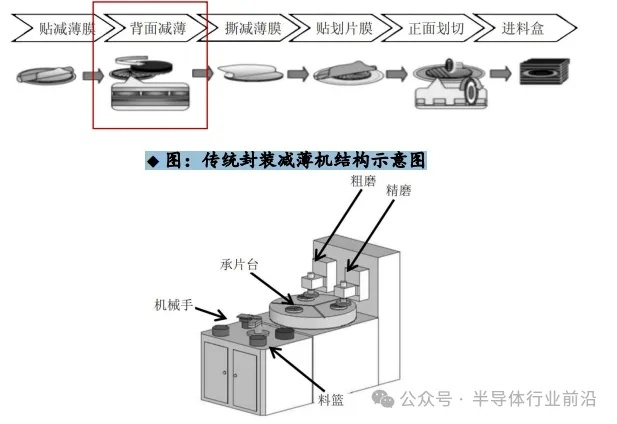

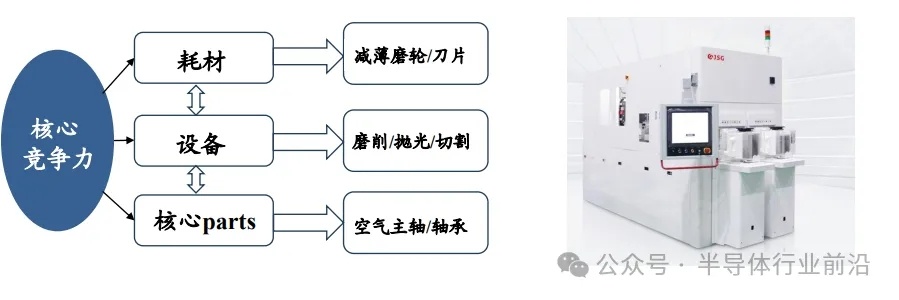

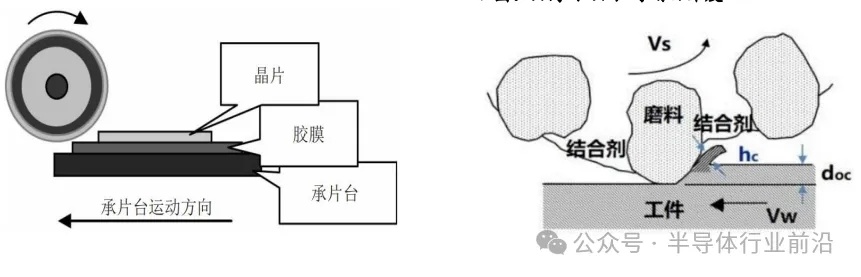

减薄机:晶圆与磨轮(砂轮)通过相对运动实现磨削减薄

减薄指的是晶圆(正面已布好电路的硅片)在后续划片之前需要进行背面减薄(Backside grinding),目前主 要通过磨轮(砂轮)磨削晶圆背面,以降低封装高度,减小芯片体积。标准的减薄流程如下图所示。减薄机结构主要包括粗磨(讲究效率)&精磨(讲究质量)磨轮、成片台、机械手、料篮等。晶圆吸附在承 片台上,通过粗磨、精磨工位上的磨轮进行减薄,减薄完成后,通过机械手将完成加工的晶圆传输到料篮里, 然后再把整个料篮拿到撕贴膜一体机上,去撕除贴在晶圆表面的保护膜,并粘贴上划片膜,为后续划切工艺 做好准备。

图8:传统封装减薄机构示意图

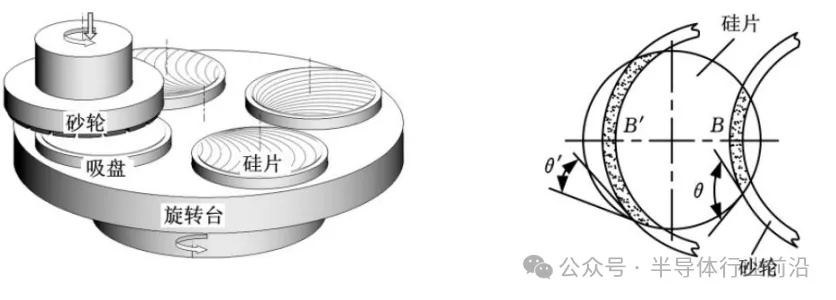

与硅片可双面减薄不同,晶圆的减薄加工只能选择单面(背面)加工方法,可分为转台式磨削(Rotary Grinding)和硅片旋转磨削(In-Feed Grinding)两种方式,两种方式的最大差异在于晶圆是否自转。

转台式磨削为磨轮转动,但晶圆自身并不自转。转台式磨削与晶圆分别固定于旋转台的吸盘上,在转台的带 动下同步旋转,晶圆本身并不绕其轴心转动,砂轮高速旋转的同时沿轴向进给,砂轮直径大于晶圆直径。⚫ 转台式磨削有整面切入式(Face Plunge Grinding)和平面切向式 (Face Tangential Grinding)两种,区别在 于磨轮是否能完全覆盖晶圆。整面切入式加工时,砂轮宽度大于晶圆直径,砂轮主轴沿其轴向连续进给直至 余量加工完毕,然后晶圆在旋转台的带动下转位;平面切向式磨削加工时,砂轮沿其轴向进给,晶圆在旋转 盘带动下连续转位,通过往复进给方式(Reciprocation)或缓进给方式(Creep Feed)完成磨削。⚫ 该种方法下实际磨削区面积 B 和切入角θ(砂轮外圆与硅片外圆之间夹角)均随着砂轮切入位置的变化而变化, 导致磨削力不恒定,TTV值较高、容易塌边、崩边,转台式磨削不适合300mm(12英寸)以上单晶硅片的磨 削加工。

图8-1:转台式摩削(平面切向式)原理示意图(左);转台式磨削的实际磨削区和切入角θ一直在变化 (右)

全球减薄设备主要由日本企业主导, CR3高达85%。全球减薄机厂商主要包括日本DISCO、东京精密、G&N、Okamoto Semiconductor Equipment Division等,减薄机头部公司DSICO、东京精密的单台设备在300~500万人民币左右,且该设备全自动化程度非常高,国内目前制造减薄机的厂商很少,包括个别研究所,如郑州第三研磨所、中电科,还有华海清科、迈为股份、 晶盛机电等,国产减薄机价格也在300万人民币左右,一台减薄机一年产能在6万片左右,也与实际研磨量有关。

晶盛在半导体的定位大硅片、先进封装、先进制程、碳化硅三代半导体等领域,半导体设备产业链逐步完 整,将形成覆盖生长、切片、抛光、外延四大核心装备为主的产品体系。(1)大硅片领域:单轴-8寸减薄 机、单轴-12寸减薄机已批量出货;(2)SiC领域:SIC减薄机已批量出货;在SOI、功率半导体领域内, Si-8寸减薄机、双轴-12寸减薄机均已批量出货;

图9:晶盛机电的单轴-12寸Si减薄机

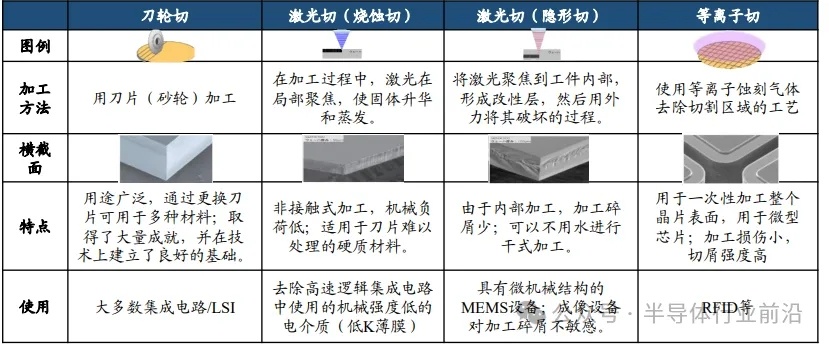

划片机:分为砂轮切、激光切,目前砂轮切为主流

一个晶圆通常由几百个至数千个 芯片连在一起。它们之间留有80um 至150um的间隙,此间隙被称之为划片 街区(Saw Street);将每一个具有独立电气性能的芯片分离出来的过程叫做划片或切割(Dicing Saw)。可分为砂轮切割和激光切割两种方式。砂轮切割是目前应用最为广泛的一种划片方式。主要采用金刚石颗粒和粘合剂组成的刀片,经主轴联动高速 旋转,与被加工材料相互磨削,并以一定速度进给将晶圆逐刀分割成独立芯片。在工艺过程因残余应力和机 械损伤导致的崩裂等缺陷,是制约砂轮划片发展的主要问题。

图10:砂轮切割原理(左);刃厚 、刃长与划切深度(右)

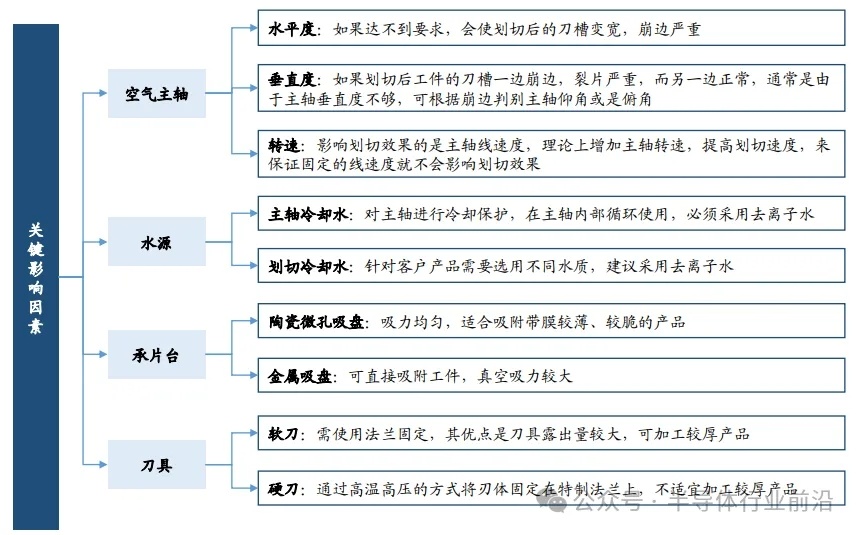

影响切片质量的关键因素包括主轴、水源、承片台、刀具等。

随着器件进一步缩小,激光切有望成为下一代主流。随着芯片特征尺寸的不断缩小和芯片集成度的不断提高,特别是在超薄硅晶圆、低k介质晶圆领域,砂轮划 片容易带来崩裂、膜层脱落等问题,激光切割可避免上述问题,同时在小尺寸及 MEMS 芯片方面,凸显出 愈发重要的优势,激光切割主要可分为激光隐形切割和激光烧蚀切割两种。

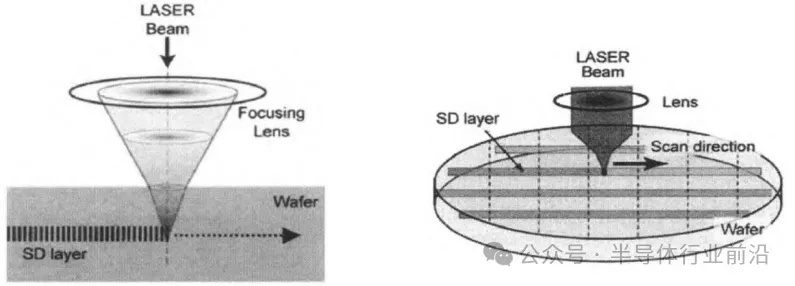

(1)激光隐形切割:隐形切割技术是将半透明波长的激光束通过光学聚焦透镜聚焦于晶圆内部,在晶圆内 部形成分割用的起点,即改质层,再对晶圆施加外力将其分割成独立芯片的技术,一般包括激光切割和芯 片分离两个过程。一方面隐形切割只作用于晶圆内部,产生碎屑有限,同时非接触加工可有效避免砂轮切 割时的损伤崩边;同时隐形切割不会造成划片间道的损失,可以提高晶圆利用率。

图11:激光束设计及改质层形成原理(左);晶圆激光隐形切割示意(右)

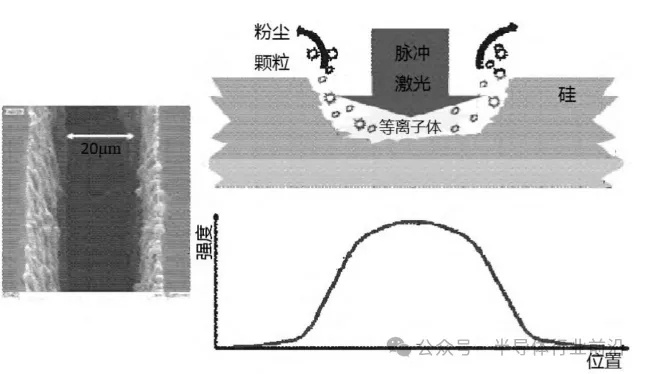

(2)激光烧蚀切割:利用高能脉冲激光,经光学系统准直和聚焦后,形成能量密度高、束斑尺寸只有微米 级的激光束,作用于工件表面,使被照射区域局部熔化、气化,从而使划片间道材料去除,最终实现开槽或 直接划透。激光烧蚀切割以高温为作用机理,在烧蚀边缘会形成被加工材料频繁重铸等现象的热影响区域, 关键在于如何控制热影响区大小。根据所加工材料对不同波长激光的吸收特性,选择相应激光器和光学系统。

图12:激光烧蚀切割基本原理

图13:各类切片机技术对比

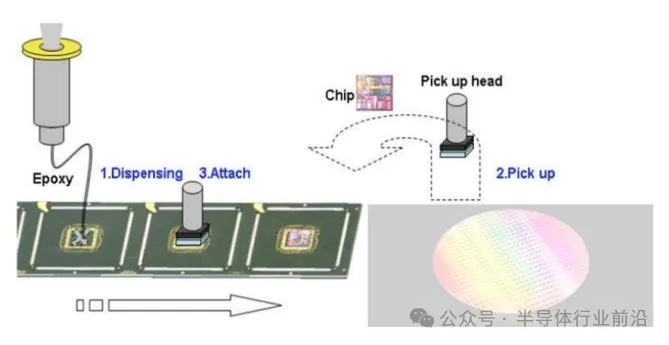

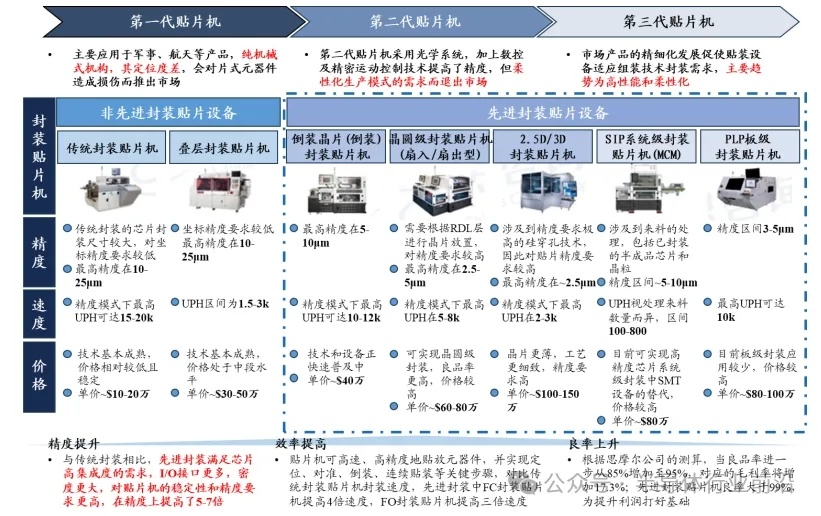

贴片机:主要起到抓取、贴放芯片作用

贴片机(Die bonder),也称固晶机,将芯片从已经切割好的晶圆(Wafer)上抓取下来,并安置在基板对 应的Die flag上,利用银胶(Epoxy)把芯片和基板粘接起来。贴片机可高速、高精度地贴放元器件,并实现 定位、对准、倒装、连续贴装等关键步骤。固晶机主要由点胶系统、物料传输系统、固晶系统、视觉系统组成。首先由点胶系统在封装基板对应位置上 进行点胶,而后固晶系统与物料传输系统相互配合,从蓝膜上精确地拾取芯片,准确地将芯片放置在封装基 板涂覆了粘合剂的位置上;接着对芯片施加压力,在芯片与封装基板之间形成厚度均匀的粘合剂层;在承载 台和物料传输系统的进给/夹持机构上,分别需要一套视觉系统来完成芯片和封装基板的定位,将芯片位置 的精确信息传递给运动控制模块,使运动控制模块能够在实时状态下调整控制参数,完成精确固晶。

图14:贴片机作业原理

设备主要性能指标为贴片精度和贴片效率。目前大部分贴片机要么满足高精度贴片,要么为高效率贴片,同时 满足两项指标是当前面临的挑战。贴片机主要性能指标受到精确的视觉对位系统、合理的结构布局、精密的运 动控制和完善的系统软件等影响。

图15:贴片机三代发展

国外固晶机单台售价500万人民币左右,国产固晶机300万人民币左右。 贴片机在细分领域国产化率呈现两极分化态势,IC贴片机因更注重小尺寸精度要求,开发难度较大,国产化率较低;LED贴片机则更重视固晶效率和良率,国产化在成本上更具优势,国产化率已超90%。

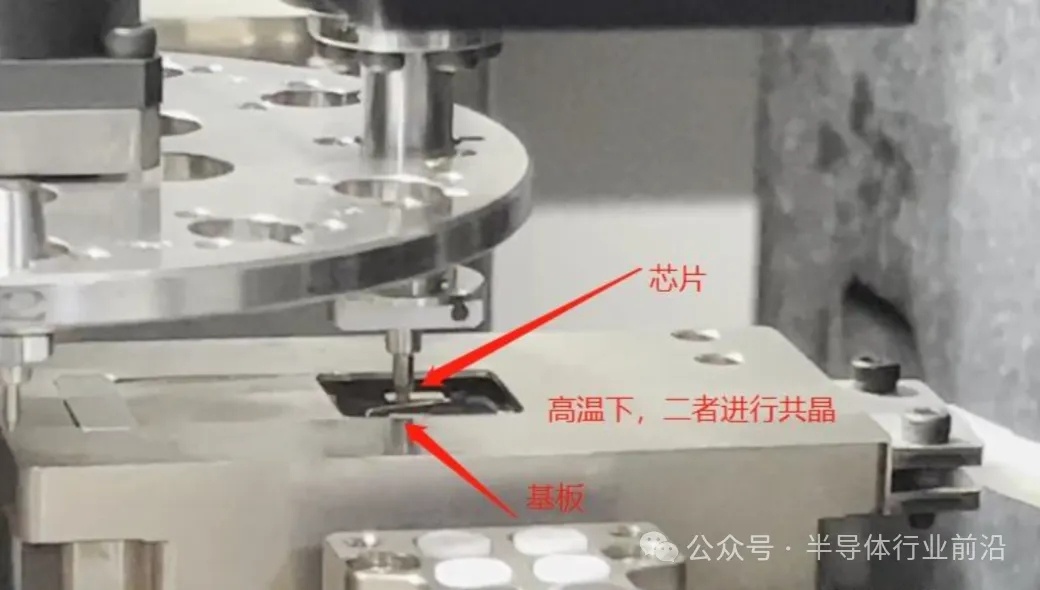

共晶机:

什么是共晶?和固晶有什么区别?

首先,我们先来区分一下“共晶”和“固晶”的概念。共晶是指在特定配比下,两种或两种以上成分的物质在固态条件下形成均匀混合的状态。在这种状态下,各个成分相互溶解,并且形成具有特定晶体结构的共晶相。共晶的形成通常与熔融和再结晶过程相关,其中原材料被熔化并通过适当的冷却速度使其固化为具有共晶结构的晶体。而固晶一般是指的环氧贴片(有时被称为环氧贴片粘结),是指物质从液态转变为固态的过程。当物质被冷却至其凝固点以下时,分子或原子会开始重新排列并结合在一起,形成具有固定空间结构的晶体。固晶过程中,原子或分子以有序的方式排列,并逐渐形成晶格。晶格的不同形状和尺寸决定了固体结晶的形态和特性。由此可得,共晶和固晶都是与物质在固态下的结构和变化有关,但共晶强调不同成分共存的状况,而固晶更侧重于物质从液态到固态的相变过程。

今天我们主要讲一下共晶机,共晶机主要用于合金材料的制备,其通过控制温度和成分比例,使合金在共晶温度下迅速凝固并形成共晶结构。

图16:共晶过程

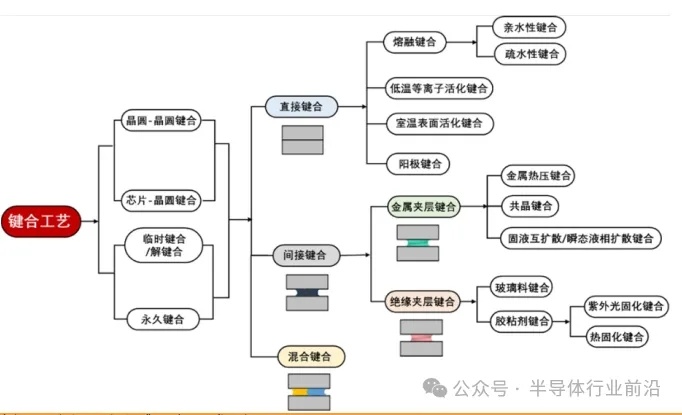

键合机:种类多元,主要将两片晶圆进行结合

键合(Bonding)是通过物理或化学的方法将两片表面光滑且洁净的晶圆贴合在一起,以辅助半导体制造工 艺或者形成具有特定功能的异质复合晶圆。键合技术有很多种,通常根据晶圆的目标种类可划分为晶圆-晶 圆键合(Wafer-to-Wafer,W2W)和芯片-晶圆键合(Die-to-Wafer,D2W);根据键合完成后是否需要解 键合,又可分为临时键合(Temporary Bonding)和永久键合(Permanant Bonding);根据待键合晶圆间 是否引入辅助界面夹层,还可分为直接键合键合、间接键合、混合键合(Hybrid Bonding)等;根据传统和 先进与否,传统方法包括引线键合(Wire Bonding),先进方法采用倒装芯片键合(Flip Chip Bonding)、 混合键合等。

数据来源:《异质集成核心工艺晶圆键合综述》,东吴证券研究所

图17:键合机种类多样

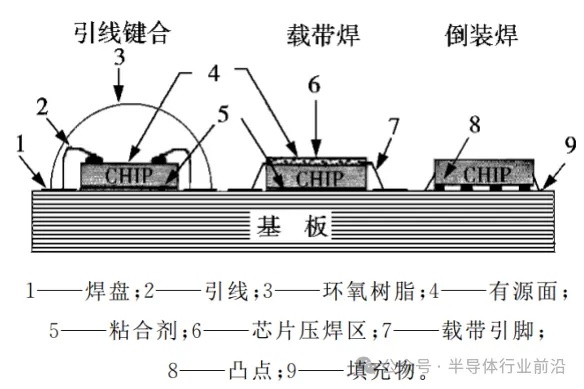

电子元件中芯片直接粘合在基板上,芯片内部输入和输出之间的互联就需要用到键合,包括三种方式——引 线键合、载带自动键合和倒装芯片键合。(1)引线键合(Wire Bonding)是用金属丝将集成电路芯片上的 电极引线与集成电路底座外引线连接在一起的过程,是目前应用最广泛的一种键合方式。(2)载带自动键 合(TAB,Tape Automated Bonding):随着WB无法适应电子整机高密度、超小超薄、芯片尺寸和焊区越 来越小而出现的,包括芯片焊区凸点形成、载带引线制作、内引线焊接、基板粘接和外引线焊接等。(3) 倒装芯片键合(FCB,Flip Chip Bonding):芯片面朝下、将芯片焊区和基板焊区直接互连的键合方法,一 般先将芯片的焊区形成一定高度的金属凸点后再倒装焊到基板焊区上。

图18:引线键合、载带焊、倒装焊

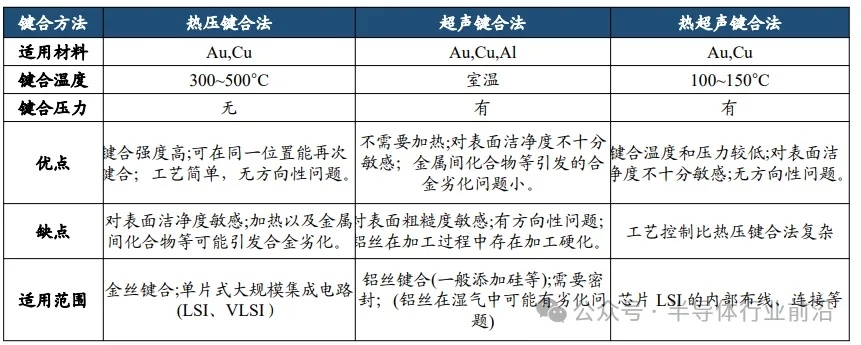

引线键合根据键合能量使用的不同可以分为热压键合法、超声键合法和热超声键合法。(1)热压键合法:利用微电弧使键合丝的端头熔化成球状,通过送丝压头压焊在引线端子上形成第一键合点;而后送丝压头 提升移动,在布线板对应的导体布线端子上形成第二键合点,完成引线连接过程。(2)超声键合法:超 声键合法主要应用于铝丝的引线连接,超声波能量被铝丝中的位错选择性吸收,使铝丝在非常低的外力作 用下可处于塑性变形状态,铝蒸镀膜表面上形成的氧化膜被破坏,露出清洁的金属表面,便于键合。(3) 热超声键合法:在超声键合机中引入加热器辅助加热,键合工具采用送丝压头,并进行超声振动,具有更 高的效率和更广泛的用途,但是工艺过程较复杂。

图19:三种引线键合方法的比较

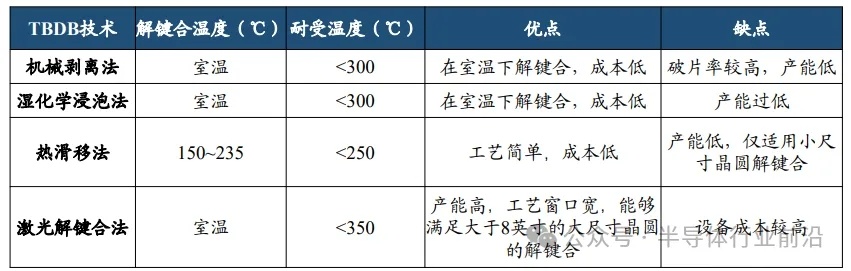

临时键合&解键合(TBDB,Temporary bonding and debonding) 是处理超薄晶圆背面制程工艺的关键支撑手段。晶圆朝着大尺寸、多芯片堆叠和超薄化方向发展,晶圆减薄(低于 100μm)主要是为了满足 TSV 制 造和多片晶圆堆叠键合总厚度受限的需求,但大尺寸薄化晶圆的柔性和易脆性使其很容易发生翘曲和破损, 为了提高芯片制造的良率、加工精度和封装精度,需要一种支撑系统来满足苛刻的背面制程工艺(如光刻、 刻蚀、钝化、溅射、电镀、回流焊和划切工序等)。在此背景下临时键合与解键合应运而生,根据解键合方式的不同,临时键合和解键合主要分为机械剥离、湿 化学浸泡、热滑移和激光解键合4种方法。

图20:不同 TBDB 技术的总结

海外K&S(库力索法)、Hesse、ASM为半导体键合机龙头。国外龙头单台售价25万美金/台(按照2024年4月13日汇率7.24计算,对应人民币约180万元),国产设备130万人民币左右。全球晶圆键合设备 消费市场主要集中在中国、日本、欧洲和美国等地区,其中中国半导体行业发展较快,晶圆键合设备销量份额最大,

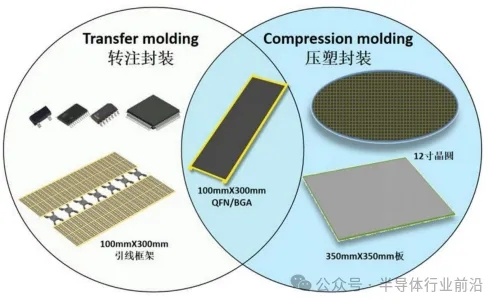

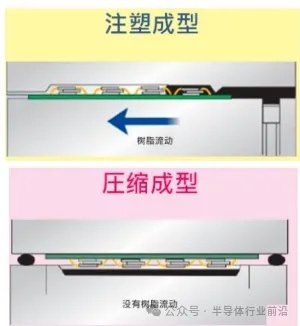

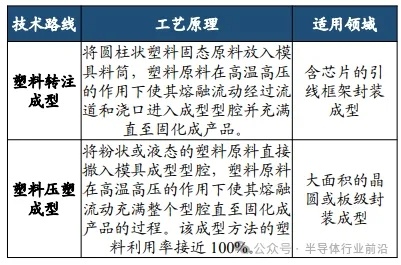

塑封机:转注封装主要用于传统封装,压塑封装主要用于先进封装

塑封机能够将芯片可靠地封装到一定的塑料外壳内,可 分为转注封装与压塑封装,先进封装背景下压塑封装为 未来趋势。转注封装成型主要用于含芯片的引线框架封 装成型,压塑封装成型主要用于大面积的晶圆或板级封 装成型,但两者也有封装产品的交集,如含芯片的框架 或基板较大面积的封装成型,如 100mmX300mm QFN 或 BGA 封装成型,所以两种成型方式不是孤立的。但 随着生产效率越来越高、芯片小型化和扁平化的发展趋势,压塑封装将是发展的方向。

图21:转注封装主要用于传统封装,压塑封装主要用于先进封装

图22:转注封装与压塑封装的区别对比

图23:转注封装与压塑封装的区别对比

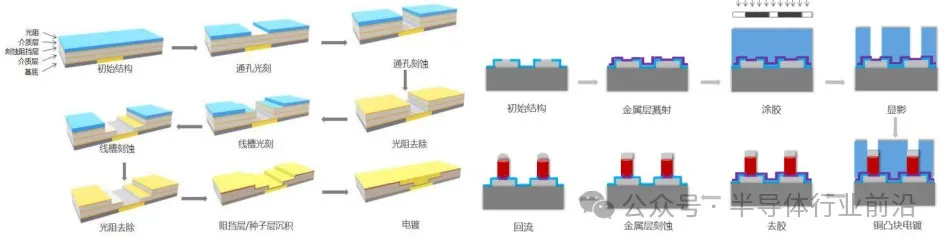

电镀机:有望受益于TSV、凸块等快速放量

电镀机:是指在芯片制造过程中,将电镀液中的金属离子电镀到晶圆表面形成金属互连。随着芯片制 造工艺越来越先进,芯片内的互连线开始从传统的铝材料转向铜材料,半导体镀铜设备便被广泛采用。目前 半导体电镀已经不限于铜线的沉积,还有锡、锡银合金、镍、金等金属,但是金属铜的沉积依然占据主导地 位。铜导线可以降低互联阻抗,降低器件的功耗和成本,提高芯片的速度、集成度、器件密度等。过去传统封装工艺中电镀机主要在封装体的特定部位上沉积金属层,例如增加引脚的导电性或在封装体外壳 上提供一层防护层,随着先进封装发展,例如凸块、 RDL、 TSV等均需要电镀金属铜进行沉积,电镀设备 有望充分受益。前道的电镀需要在晶圆上沉积一层致密、无孔洞、无缝隙等其他缺陷,并且分布均匀的铜, 再配以气相沉积设备、刻蚀设备、清洗设备等,完成铜互连线工艺;后道来看,在硅通孔、重布线、凸块工 艺中都需要金属化薄膜沉积工艺,使用电镀工艺进行金属铜、镍、锡、银、金等金属的沉积。

图24:芯片制造前道铜互连电镀工艺示意图 (左);芯片制造后道先进封装电镀工艺示意图(右)

其中前道晶圆制造的电镀设备领域,目前全球市场主要被 LAM 垄断;后道先进封装电镀设备领域, 全球范围内的主要设备商包括美国的AMAT和 LAM、日本的 EBARA 和新加坡 ASM Pacific 等;国内企业 中盛美半导体较为领先。

本文转载自:半导体行业观察

转载内容仅代表作者观点

不代表上海隐冠半导体立场