(图片来源自网络)

套刻误差的定义是两层图形结构中心之间的平面距离。随着集成电路的层数不断增多,多重图形和多重曝光的光刻工艺被广泛应用,不同步骤形成的电路图形之间的套刻精度愈发重要。套刻误差过大形成的错位,会导致整个电路失效报废。套刻误差测量设备,用于确保不同层级电路图形,和同一层电路图形的正确对齐和放置。套刻误差测量通常在每道光刻步骤后进行。

套刻误差测量有光学显微成像(IBO)、光学衍射成像(DBO)、扫描电子显微镜(SEM-OL)三种方法。光学显微成像设备比较常用,通过光学显微系统获得两层套刻目标图形的数字化图形,然后通过软件算法定位每一层图形的边界位置,进一步计算出中心位置,从而获得套刻误差;光学衍射设备将一束单色平行光,照射到不同层套刻目标的光栅上,通过测量衍射射束强度的不确定性来确定误差。扫描电子显微镜的主要用于刻蚀后的最终套刻误差测量,对应的目标图形尺寸更小,但测量速度较慢。

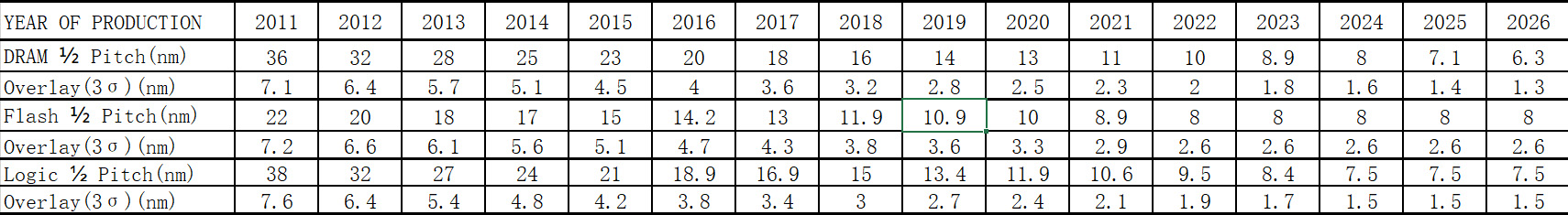

国际半导体技术路线图(international technology roadmap for semiconductor,ITRS)对每一个技术节点的光刻工艺都提出了套刻误差的要求,如表1所示。从表中可以看出,随着技术节点的推进,关键光刻层允许的对准偏差(即套刻误差)是以大约80%的比例缩小。例如,20nm节点中关键层的套刻误差要求(mean+3σ)是8.0nm。

表1 每一个技术节点允许的套刻误差 (图片来源自网络)

隐冠半导体基于其强大的研发能力,可提供静态抖动2nm,最大加速度20m/s²的高端运动平台。为进一步提高运动平台的性能,确保其卓越的运动整定表现,我们可以提供配套的高性能主动减振解决方案。此外,我们还可以提供定制化的、静态抖动达2nm的压电垂向运动系统。隐冠半导体拥有覆盖全国主要城市的售后团队,为您提供全方位的技术支持。